안녕하세요 오늘은 간단하게 Verilog HDL 언어를 tool로 어떻게 사용하는지 알아보겠습니다.

1. Vivado 설치

먼저 vivado를 다운로드 해주셔야 하는데 xilinx 홈페이지에서 다운로드 할 수 있습니다.

다운로드를 진행할 때 아이디가 필요하니 회원가입 후 다운로드를 진행해주시면 됩니다.

https://www.xilinx.com/support/download.html

Downloads

Vivado, Vitis, Vitis Embedded Platform, PetaLinux, Device models

www.xilinx.com

2. Vivado Project 생성

Vivado 설치를 완료하셨으면 Vivado를 실행시켜줍니다. 실행시켜주면 아래와 같은 화면이 뜨게되는데 간단한 Project를 만들어보겠습니다. 먼저 새로 프로젝트를 만들어보겠습니다. 초록색 박스 안에 있는 Create Project를 눌러주세요.

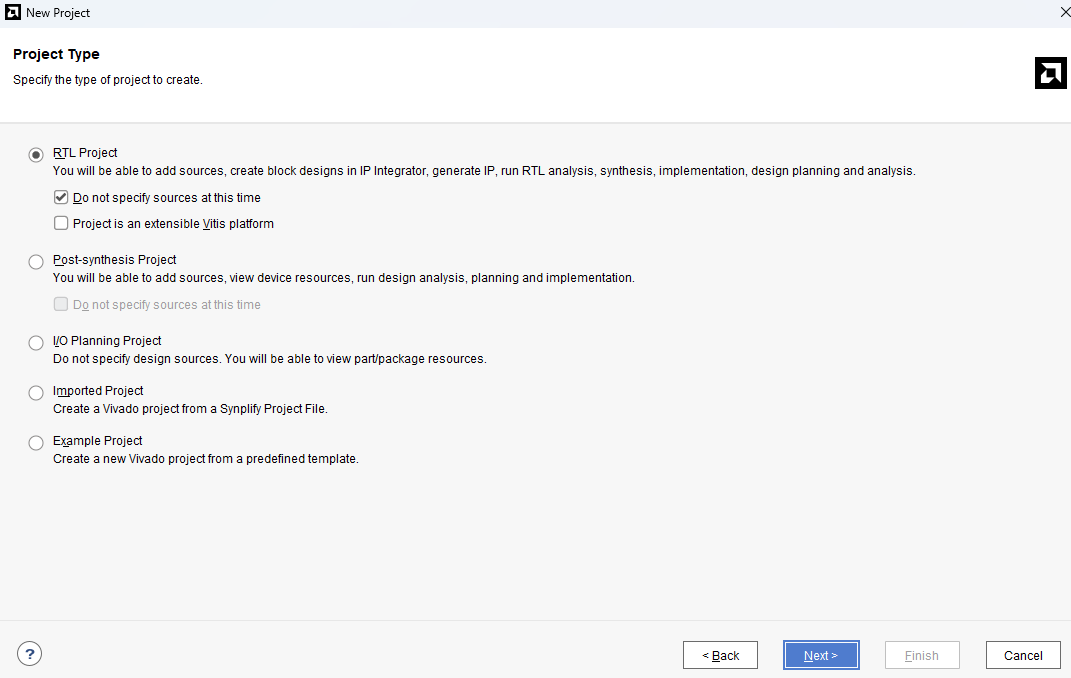

Project를 생성후 절차에 따라서 진행하면 되는데 Project Type에서 다양한 유형의 Project를 선택할 수 있는데 궁금하신 분들을 위해 아래 <더보기>를 누르시면 보실 수 있습니다.

RTL Project

RTL (Register Transfer Level) 프로젝트로, 디지털 회로를 IP Integrator를 사용해 블록 설계를 만들거나, Verilog나 VHDL 같은 HDL(Hardware Description Language)을 사용하여 설계하고 실제로 구현하는 과정입니다. IP 생성, RTL 분석, 합성, 구현, 설계 계획 및 분석 등을 수행할 수 있습니다. 이 옵션은 프로젝트가 확장 가능한 Vitis 플랫폼으로 설정할 수도 있습니다.

Post-synthesis Project

합성 이후의 프로젝트로, 주로 이미 합성된 디자인에 대해 리소스 보기, 재합성, 분석, 계획 및 구현 작업을 수행합니다. 이 프로젝트 유형은 합성이 완료된 후 최적화와 분석을 중점적으로 다룹니다.

I/O Planning Project

I/O (Input/Output) 플래닝 프로젝트로, 디자인 소스를 지정하지 않고 핀 배치나 패키지 자원을 계획할 수 있습니다.

주로 하드웨어의 물리적 구성과 연결에 초점을 맞춥니다.

Imported Project

이미 완성된 다른 프로젝트 파일에서 Vivado 프로젝트를 생성합니다. 예를 들어 Simplify Project 파일에서 직접 프로젝트를 가져올 수 있습니다.

Example Project

Vivado가 제공하는 미리 정의된 템플릿을 바탕으로 새로운 프로젝트를 생성합니다.초보자나 학습 목적으로 유용하며, 예제를 통해 다양한 기능을 신속하게 배울 수 있습니다.

여러 옵션 중에서 RTL Project를 선택해줍니다.

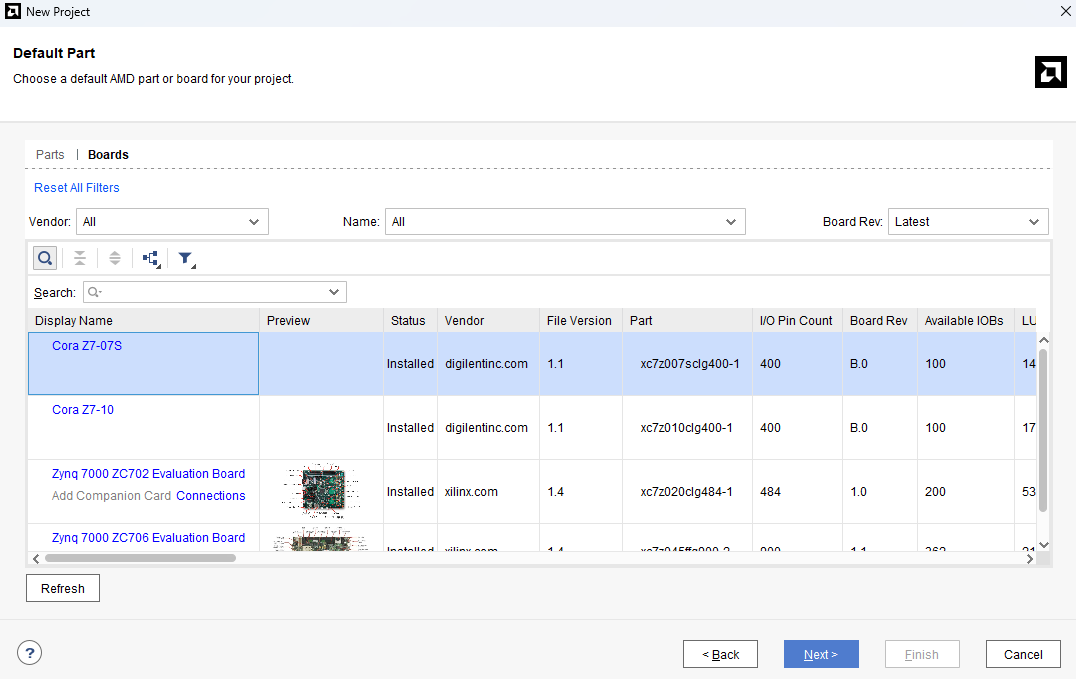

다음은 사용하시는 Board를 지정하고 Next를 눌러주시면 됩니다. 설정이 모두 완료되었으면 마지막으로 Finish를 눌러주세요.

프로젝트를 성공적으로 만들면 이러한 메인 화면이 나오게 됩니다.

본격적으로 만들기 전에 먼저 Flow Navigator에 있는 용어를 먼저 알아보고 가겠습니다.

(더보기)

1. PROJECT MANAGER

- Settings: 프로젝트의 전반적인 설정을 변경할 수 있습니다. FPGA 보드 선택, 합성 옵션, 타이밍 제약 등 다양한 설정을 지정할 수 있습니다.

- Add Sources: 프로젝트에 필요한 소스 파일을 추가합니다. Verilog, VHDL, 제약 파일 등을 포함할 수 있습니다.

- Language Templates: 다양한 HDL(하드웨어 설명 언어) 및 스크립트 언어의 코드 스니펫을 제공합니다. 빠르게 코드를 작성할 때 유용합니다.

- IP Catalog: 사용 가능한 IP(Intellectual Property) 코어를 검색하고 구성할 수 있는 카탈로그입니다. IP는 특정 기능을 미리 구현해 둔 모듈로, 사용자가 디자인을 빠르게 진행할 수 있도록 도와줍니다.

2. IP INTEGRATOR

- Create Block Design: 새로운 블록 디자인을 생성합니다. IP 코어들을 드래그 앤 드롭으로 쉽게 연결하고 구성할 수 있습니다.

- Open Block Design: 저장된 블록 디자인을 열어 수정할 수 있습니다.

- Generate Block Design: 블록 디자인을 바탕으로 필요한 HDL 파일들을 자동으로 생성합니다.

3. SIMULATION

- Run Simulation: 설정한 테스트 벤치와 디자인을 사용하여 시뮬레이션을 실행합니다. 이는 디자인이 의도한 대로 동작하는지 검증하는 중요한 단계입니다.

4. RTL ANALYSIS

- Run Linter: HDL 코드의 문법 오류나 스타일 가이드를 체크합니다. 좋은 코딩 관행을 유지하는 데 도움을 줍니다.

- Open Elaborated Design: RTL 디자인이 elaboration 단계를 거쳐서 더 상세하게 표현된 디자인을 볼 수 있습니다. 여기서는 Schematic View를 통해 연결과 구조를 확인할 수 있습니다.

5. SYNTHESIS

- Run Synthesis: HDL 코드를 FPGA의 물리적 구조에 맞는 넷리스트로 변환하는 과정입니다. 이 과정을 통해 타이밍 분석과 최적화가 수행됩니다.

- Open Synthesized Design: 합성된 디자인을 열어보고, 문제가 있는 부분을 진단하고 최적화할 수 있습니다.

6. IMPLEMENTATION

- Run Implementation: 합성된 넷리스트를 실제 FPGA 칩의 물리적 리소스에 매핑하는 과정입니다. 플레이스먼트(위치 결정)와 라우팅(연결 경로 결정)을 포함합니다.

- Open Implemented Design: 구현된 디자인을 검토하여, 물리적 배치와 연결 상태를 확인하고 최적화할 수 있습니다.

7. PROGRAM AND DEBUG

- Generate Bitstream: 최종 디자인에서 비트스트림을 생성합니다. 비트스트림은 FPGA에 프로그래밍하기 위한 바이너리 파일입니다.

- Open Hardware Manager: 하드웨어 매니저를 통해 FPGA 보드에 비트스트림을 다운로드하고 디버깅할 수 있습니다.

3. Source File 생성

먼저 소스 파일을 생성해야 하는데 Project Manager에서 Add source를 눌러서 추가합니다.

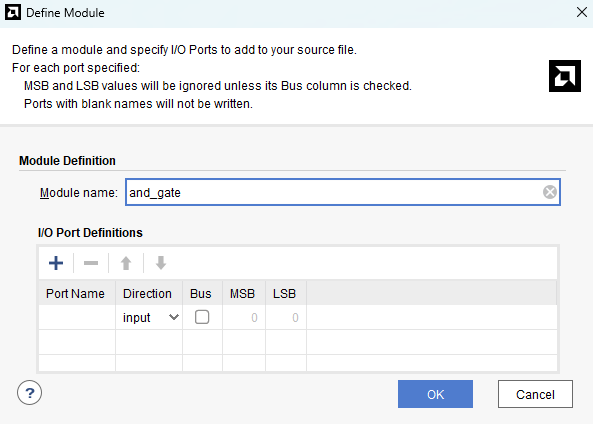

create File을 눌러주고 이름을 정해줍니다. 모듈은 해당 옵션에서 Input / Output을 지정해줘도 되고 생성 후 직접 지정을 해줘도 됩니다.

완료하면 다음과 같은 화면이 나타납니다. 해당 source file을 클릭하면 veilog HDL을 입력할 수 있는 창이 나타납니다.

기본적으로 하나의 모듈로 구성이 되어 있고 간단하게 and gate를 만들어보겠습니다.

input으로 a와 b가 선언되었으며, output으로는 y가 출력되었습니다. a와 b 모두 신호가 1일때만 y에 1을 할당하는 And Gate 모듈을 만들었습니다.

timescale

여기서 timescale 지시어는 Verilog HDL에서 시뮬레이션의 시간 단위와 해상도를 정의하는 데 사용되는 코드입니다.

1ns / 1ps에서 1ns는 시간의 단위 (time unit)이고, 1ps는 시간의 정밀도인데 시간 단위는 시간을 측정하는 기본 단위이며 시간 관련 계산은 나노초를 기준으로 표현합니다. 시간 정밀도는 시뮬레이터가 인식할 수 있는 최소 시간 변화량을 나타내며 여기서는 피코초(ps) 입니다. 시뮬레이션 동안 시간을 피코초 단위로 미세하게 측정할 수 있음을 의미합니다.

간단한 비유로, 생각해보면, 시간 단위는 자동차의 속도계가 km/h를 사용하는 것과 비슷하고, 시간 정밀도는 속도계가 소수점 아래까지 얼마나 정밀하게 측정하는지와 유사합니다.

Assign

assign 문은 Verilog HDL에서 연속 할당을 정의하는 데 사용됩니다. 연속 할당은 출력이 입력의 상태에 따라 언제든지 자동으로 업데이트되도록 하는 방식입니다. 이는 입력 신호가 변경될 때마다 출력 신호도 즉시 변경되도록 합니다.

assign 문을 사용하면 입력의 변화가 있을 때마다 실시간으로 출력에 반영됩니다. 이 모듈에서는 입력 a와 b의 논리적 AND 연산 결과가 항상 출력 y에 할당됩니다. 만약 a 또는 b의 값이 변경되면, y의 값도 즉시 그 결과에 따라 갱신됩니다.

4. TestBench 생성

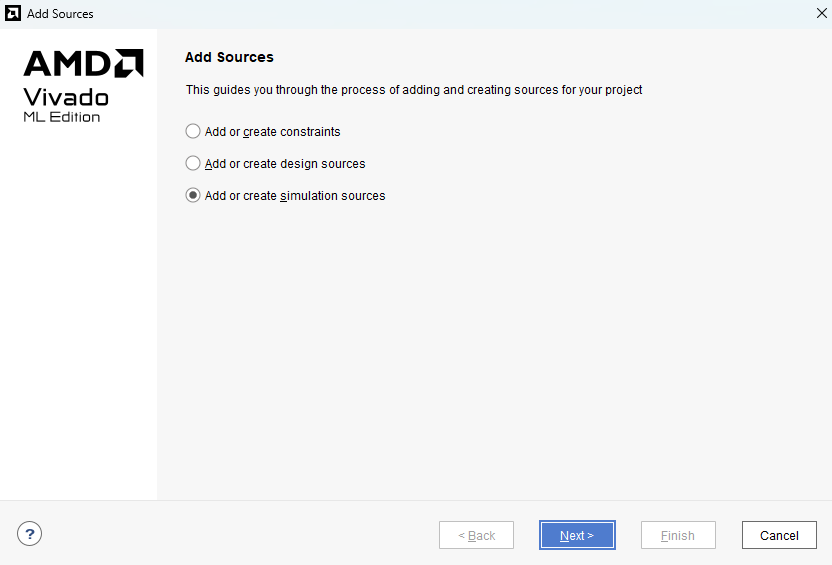

이번엔 결과값을 테스트 하기 위해 Testbench를 만들어보겠습니다.

이번엔 Simulation을 선택한 후 같은 방법으로 만들어줍니다.

- 변수에서 reg 타입와 wire 타입이 사용되었는데 reg 타입은 테스트 벤치에서 값을 수동으로 제어할 수 있게 해주며, wire 타입은 연속 할당에 사용됩니다.

- and gate 모듈을 u0라는 인스턴스 이름으로 호출하면서, 포트 연결을 통해 테스트 벤치의 a, b, y와 모듈의 a, b, y를 연결합니다.

- 입력 a와 b의 모든 가능한 조합을 순차적으로 적용합니다. 각 입력 쌍에 대해 10 나노초의 시간 지연(#10)을 두어 적용하고, 마지막 입력 후에는 20 나노초를 기다린 후 시뮬레이션을 종료합니다.

- #10은 시간 지연을 나타내며, 각 입력 조합 사이에 10나노초의 지연을 설정합니다. 이는 timescale 1ns / 1ps 지시어에 의해 나노초 단위로 적용됩니다.

5. Simulation

저장 후 simulation을 실행합니다.

10ns 간격으로 simulation이 변하는 걸 볼 수 있으며 a와 b가 모두 1일때만 y가 1로 올라가는 것을 확인할 수 있다.

6. Run Linter

Linter는 코드의 스타일과 구조를 체크하여 일관성, 잠재적인 문법 오류, 그리고 표준 코딩 관행에 어긋나는 부분을 식별합니다. 이 도구는 HDL 코드에서 일반적인 실수와 비효율적인 코딩 패턴을 지적해 주어, 코드 품질을 향상시키는 데 도움을 줍니다.

<Run Linter Menu>

Schematic을 누르면 엘라보레이티드(상세화된) 디자인의 스키매틱을 보여줍니다. 이는 디자인의 블록, 연결, 구조를 시각적으로 표현하여 디자인을 이해하고 문제를 식별하는 데 도움을 줍니다.

Report Methodology는 디자인의 구현 방법론을 분석하고 보고합니다. 이는 디자인이 표준 디자인 방법론을 따르고 있는지, 효율적인지를 평가하는 데 사용됩니다.

Report DRC (Design Rule Check)는 디자인 규칙 검사를 수행하여 디자인이 특정 기술 노드의 제조 규칙 및 제약 조건을 준수하는지 확인합니다. DRC는 물리적 구현 전에 디자인의 오류를 사전에 발견하여 수정할 수 있는 기회를 제공합니다.

Report Noise는 회로 내에서 발생할 수 있는 노이즈와 그 영향을 분석합니다. 이는 전력 노이즈, 크로스토크 등 다양한 소스로부터 발생하는 노이즈의 영향을 평가하고, 디자인의 안정성을 보장하는 데 중요합니다.

7. Synthesis

이제 합성을 진행해보도록 하겠습니다.

<Launch Runs>

Launch directory: 합성이나 구현 실행 파일이 저장될 디렉토리를 선택할 수 있습니다. Default Launch Directory는 시스템의 기본 설정 디렉토리를 사용한다는 것을 의미합니다. 사용자는 이 드롭다운 메뉴를 통해 다른 저장 위치를 선택할 수도 있습니다.

Launch runs on local host: 이 옵션을 선택하면 현재 사용 중인 컴퓨터(로컬 호스트)에서 합성 또는 구현 작업을 실행합니다.

Number of jobs: 동시에 실행할 작업의 수를 선택할 수 있습니다. 여기서는 '8'로 설정되어 있어, 최대 8개의 작업을 동시에 처리할 수 있음을 나타냅니다. 이는 합성과 구현 과정의 속도를 높이기 위해 다중 코어 또는 다중 스레드 처리 능력을 활용하는 옵션입니다.

Generate scripts only: 이 옵션을 선택하면 실제로 작업을 실행하지 않고, 실행에 필요한 스크립트만 생성합니다. 이는 작업을 수동으로 제어하거나 다른 환경에서 실행하고자 할 때 유용합니다.

합성 시간은 컴퓨터, 노트북 등 기기가 가진 사양에 따라서 달라집니다. 합성을 시작하게 되면 오른쪽 상단에 해당 사진처럼 진행 표시가 뜨게 됩니다.

합성을 완료하면 기본적으로 Open Systhesiszed Design에 사용할 수 있는 기능들이 생성이 되는데 여기서는 간단하게 Schematic과 Rport Utilization만 보도록 하겠습니다.

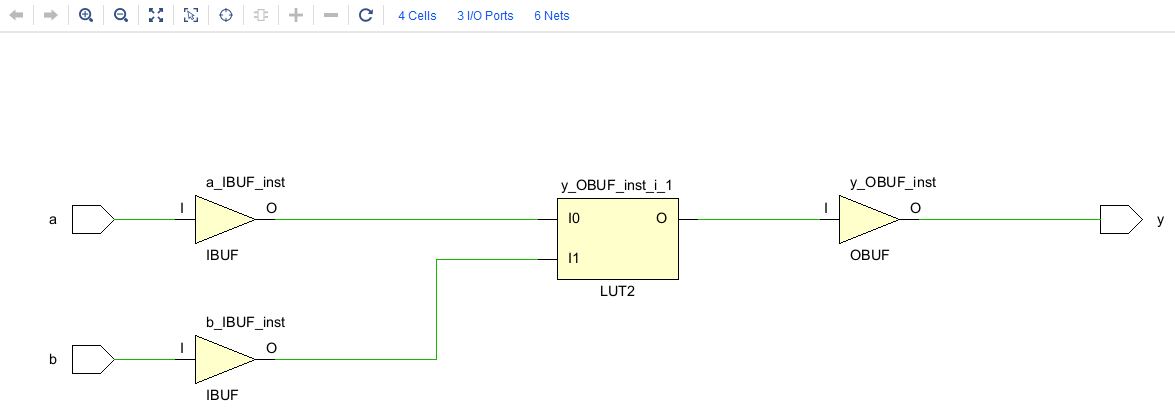

Schematic

Schematic은 합성된 디자인의 시각적인 표현을 제공합니다. 이 옵션을 선택하면, FPGA 디자인의 모듈, 연결, 및 계층 구조를 그래픽 형태로 볼 수 있습니다. 스키매틱 뷰는 디자인의 다양한 부분이 어떻게 서로 연결되어 있는지 이해하는 데 도움을 줍니다. a와 b라는 두 입력 신호가 IBUF를 통해 FPGA 내로 들어와 LUT2에서 특정 논리 연산을 거친 후, OBUF를 통해 y라는 결과 신호로 외부로 출력되는 과정을 보여줍니다.

다음은 BUF와 LUT에 대한 설명입니다.

IBUF (Input Buffer): 입력 버퍼(IBUF)는 외부에서 FPGA로 들어오는 신호를 버퍼링하여 내부 논리 회로에서 사용할 수 있게 합니다. 이는 외부 신호와 FPGA 내부 논리 사이의 신호 무결성과 전기적 특성을 관리하는 역할을 합니다. a 및 b는 각각 외부 입력을 받아 해당 IBUF를 통과하여 내부 논리로 전달되는 구조입니다. 각각 a_IBUF_inst 및 b_IBUF_inst로 표시되어 있습니다.

OBUF (Output Buffer): 출력 버퍼(OBUF)는 FPGA 내부의 논리 회로에서 생성된 신호를 외부로 전달하기 전에 버퍼링합니다. 이는 내부 신호를 외부에 안전하게 출력하는 역할을 하며, 드라이브 능력을 강화하고 신호 무결성을 보장합니다. OBUF는 LUT2의 결과를 받아 외부로 출력하는 y 신호를 생성합니다. y_OBUF_inst는 이 출력 버퍼의 인스턴스입니다.

LUT2 (Look-Up Table): LUT2는 입력 신호에 대한 간단한 논리 연산을 수행하는 FPGA의 기본적인 구성 요소입니다. 이 경우 LUT2는 두 개의 입력을 받아 하나의 출력을 생성하며, 이는 일반적으로 간단한 논리 게이트(AND, OR, XOR 등)를 구현하는 데 사용됩니다. LUT2는 a_IBUF_inst와 b_IBUF_inst로부터 오는 입력 신호를 받아 처리합니다. I0와 I1은 각각 LUT의 두 입력 포트를 나타내며, 이는 a와 b 입력에 대응됩니다.

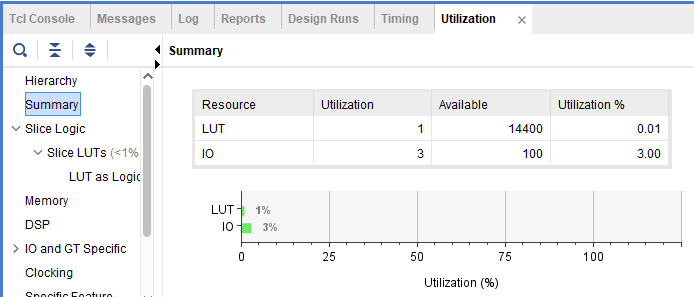

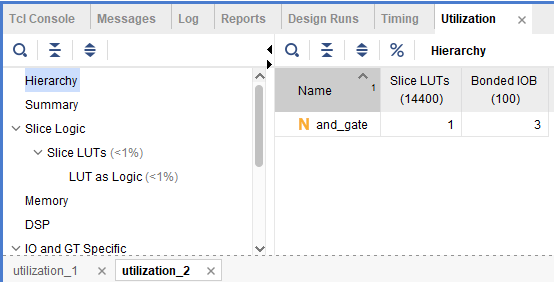

Report Utilization

Report Utilization은 합성된 디자인이 FPGA 자원을 얼마나 사용하고 있는지에 대한 상세한 보고서를 제공합니다. 이 보고서에는 LUTs(룩업 테이블), 레지스터, I/O 포트, 블록 RAM 등 FPGA의 각종 물리적 자원 사용 현황이 포함됩니다.

이 보고서를 통해 설계자는 자신의 디자인이 타깃 FPGA 내에서 얼마나 많은 공간을 차지하고 있는지, 추가 최적화가 필요한 부분은 어디인지 파악할 수 있습니다. 자원 사용률이 높을 경우, 설계를 변경하여 더 효율적으로 만들거나, 더 큰 용량의 FPGA로 이전하는 결정을 내릴 수 있습니다.

8. Implementation

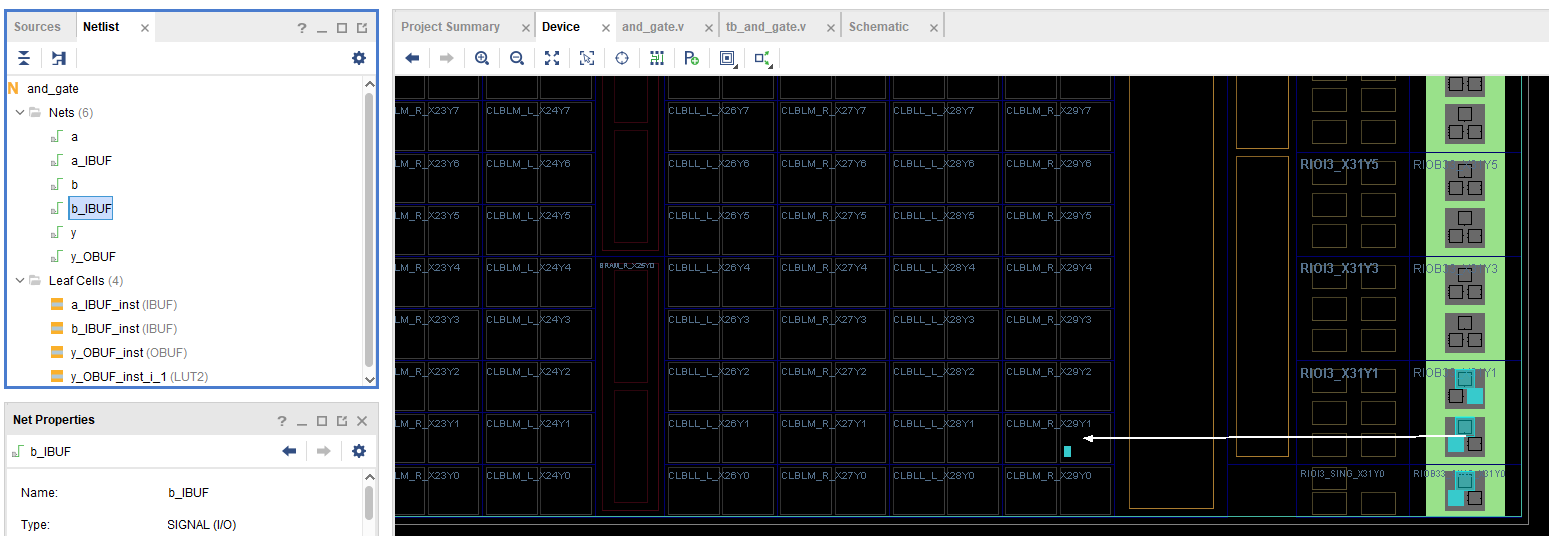

이번엔 합성된 디자인을 실제 FPGA에 올려보도록 하겠습니다.

Run Implementation을 누르면 FPGA 내의 실제 리소스를 사용하여 합성된 넷리스트를 배치(Placement)하고 연결(Routing)합니다.

구현된 디자인이 FPGA 칩의 어느 부분에 매핑되었는지를 시각적으로 표시합니다. 칩의 물리적 구조를 격자 형태로 나타내며, 각각의 격자는 FPGA의 특정 리소스(예: LUT, 레지스터, 블록 RAM 등)를 사용하는 위치를 보여줍니다.

Timing, Delay를 다루는 부분은 clk을 사용했을 때 다시 한 번 해당 메뉴에서 다뤄보도록 하겠습니다.

'하만 세미콘 아카데미 > Verilog HDL' 카테고리의 다른 글

| Verilog HDL 실습 (Counter) (1) | 2024.05.31 |

|---|---|

| Verilog HDL 실습 (1sec_LED) (0) | 2024.05.31 |

| Verilog HDL 실습 (Parity_bit) (0) | 2024.05.31 |

| Verilog HDL 실습 (Full Adder) (1) | 2024.05.31 |

| Vivado 사용법 및 간단한 실습 Part2 (D Flip Flop) (1) | 2024.05.27 |