Vivado 사용법 및 간단한 실습 Part1

https://engineeringstudentww.tistory.com/12

Vivado 설치와 프로젝트 생성 방법 등은 위 링크를 누르시면 이동됩니다. 이전에 작성했던 부분에 대해서는 중복적으로 작성하지 않도록 하겠습니다.

오늘은 D Flip Flop을 통해서 Delay 및 Timing 부분에 대해서 알아보도록 하겠습니다.

1. D Flip Flop

Digital Logic에 있어서 가장 기본이 되는 저장을 위한 Logic입니다. Flip Flop 또는 래치는 전자공학에서 1bit의 정보를 보관, 유지할 수 있는 회로이며 순차회로의 기본 요소입니다.

이전 상태를 게속 유지하여 저장하고 휘발성 메모리로 이는 전원이 나가면 저장되어 있던 값들도 사라집니다. Digital Logic 설계시, Clock을 동기화해서 설계해야 합니다. Digital 회로에서 기본이 되는 저장하는 Logic이 Flip-Flop 입니다.

D Flip-Flop은 광범위하게 사용되고 D는 Data 또는 Delay로 알려져 있다.

- 입력 D의 값을 클럭의 엣지에서 캡처해서 Q에 반영한다. (Clock의 Edge에 동기화하여 값을 업데이트 한다),

- Edge가 발생하지 않는 시간에는 Q가 변하지 않고 유지한다 (저장)

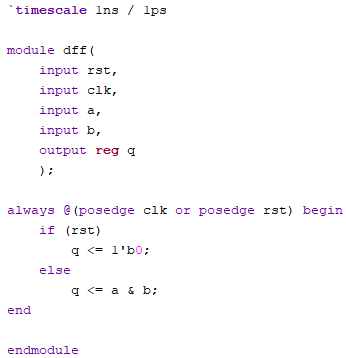

2. D Flip Flop - Source File

D Flip Flop을 Verilog HDL로 설계해보겠습니다.

always 문을 사용하여 클럭의 상승엣지 또는 리셋의 상승엣지에서 발생합니다. 리셋이 활성화되면 출력 q를 0으로 초기화 하고 리셋이 비활성화 상태일 때, a와 b의 and 연산 결과를 출력 q에 저장합니다.

테스트 벤치는 클록 신호를 생성하여 클록 주기가 20ns(10ns 간격으로 클록이 토글)이 되도록 만들고 클록의 각 상승 에지에서, 입력 a의 값을 샘플링하여 출력 q에 저장하는 과정을 시뮬레이션합니다. 입력 값 a는 클록의 상승 에지 이전에 할당되어, 플립플롭이 정확한 타이밍에 따라 동작하도록 합니다.

이 테스트 벤치를 통해 D 플립플롭의 기본적인 작동 원리인 데이터의 동기적 샘플링과 저장 과정을 검증합니다.

초기에 rst 신호를 활성화시켜 출력 q를 리셋하고, 이후 리셋을 해제한 상태에서 다양한 입력 a를 통해 q의 반응을 관찰합니다. 이러한 방식으로 플립플롭의 동작 안정성 및 신뢰성을 확인할 수 있습니다.

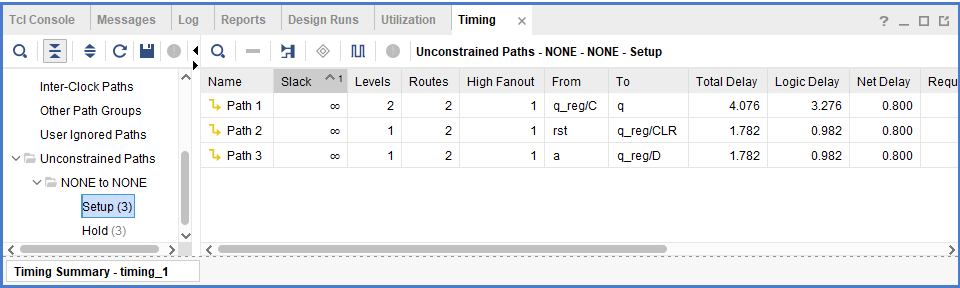

3. Report Timing Summary (Systhesis)

이번엔 Synthesis를 하여 Timing Summary를 살펴보겠습니다.

Report Timing Summary는 FPGA 또는 ASIC 설계의 타이밍 분석에서 중요한 역할을 합니다. 이 메뉴는 설계 내의 다양한 타이밍 패스를 요약하여 보여주고, 각각의 타이밍 요건을 만족하는지 여부를 검토하여 설계가 특정 클록 주파수에서 안정적으로 작동할 수 있는지 확인하는 데 필수적인 정보를 제공합니다.

합성 후의 타이밍 분석이고 각 표에 대한 내용은 아래와 같습니다.

- Name: 각 경로는 고유한 이름으로 식별됩니다 (Path 1, Path 2, Path 3).

- Slack: 각 경로에 대해 계산된 타이밍 여유를 나타냅니다. 여기에서 모든 경로의 Slack이 ∞(무한대)로 표시되어 있어, 이들 경로가 제약 없이 충분히 빠르게 동작하고 있음을 의미합니다.

- Levels: 신호가 거쳐야 하는 논리 레벨 수입니다.

- Routes: 각 경로를 구성하는 노드 수입니다.

- High Fanout: 해당 경로에 연결된 높은 팬아웃을 가진 노드 수입니다.

- From/To: 신호가 이동하는 시작점과 끝점을 나타냅니다.

- Total Delay: 경로 전체의 지연 시간(나노초).

- Logic Delay: 논리 요소들에 의한 지연 시간(나노초).

- Net Delay: 연결선에 의한 지연 시간(나노초).

각 Path Delay 비교

Path 1

From/To: q_reg/C to q - 이 경로는 플립플롭 q의 클록 입력에서 출력까지의 타이밍을 나타냅니다.

Total Delay: 4.076 ns - 전체 경로의 지연 시간입니다.

Logic Delay: 3.276 ns,

Net Delay: 0.800 ns - 논리 및 연결 지연입니다.

Path 2

From/To: rst to q_reg/CLR - 리셋 신호가 q 플립플롭의 리셋 입력까지의 경로입니다.

Total Delay: 1.782 ns - 전체 경로의 지연 시간입니다.

Logic Delay: 0.982 ns,

Net Delay: 0.800 ns - 논리 및 연결 지연입니다.

Path 3

From/To: a to q_reg/D - 데이터 입력 a에서 q 플립플롭의 데이터 입력까지의 경로입니다.

Total Delay: 1.782 ns - 전체 경로의 지연 시간입니다.

Logic Delay: 0.982 ns,

Net Delay: 0.800 ns - 논리 및 연결 지연입니다.

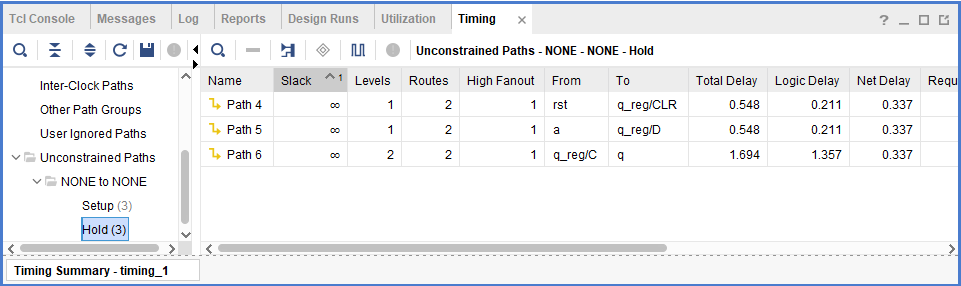

Path 4

From/To: a to q_reg/D

Total Delay: 0.510 ns

Logic Delay: 0.179 ns

Net Delay: 0.331 ns

Requirement: -∞ (무한대 음수는 제약이 없거나, 매우 느슨하게 설정되어 있음을 의미할 수 있습니다.)

Path 5

From/To: rst to q_reg/CLR

Total Delay: 0.512 ns

Logic Delay: 0.168 ns

Net Delay: 0.344 ns

Requirement: -∞

Path 6

From/To: rst to q_reg/C

Total Delay: 1.694 ns

Logic Delay: 1.357 ns

Net Delay: 0.328 ns

Requirement: -∞

이러한 정보는 설계가 클록 속도 및 타이밍 요구 사항을 충족하고 있는지 판단하는 데 중요합니다.

Slack이 무한대로 표시되어 있는 것은 현재 설정된 타이밍 제약 조건에 대해 모든 경로가 충분한 여유를 가지고 있다는 것을 의미합니다. 만약 실제 설계에서 이러한 경로들에 대한 명확한 타이밍 제약이 없다면, 타이밍 제약을 설정하여 더 정확한 타이밍 분석을 수행해야 할 필요가 있습니다. 이는 설계의 신뢰성을 확보하고, 실제 칩 제작 과정에서 발생할 수 있는 타이밍 문제를 예방하는 데 중요합니다.

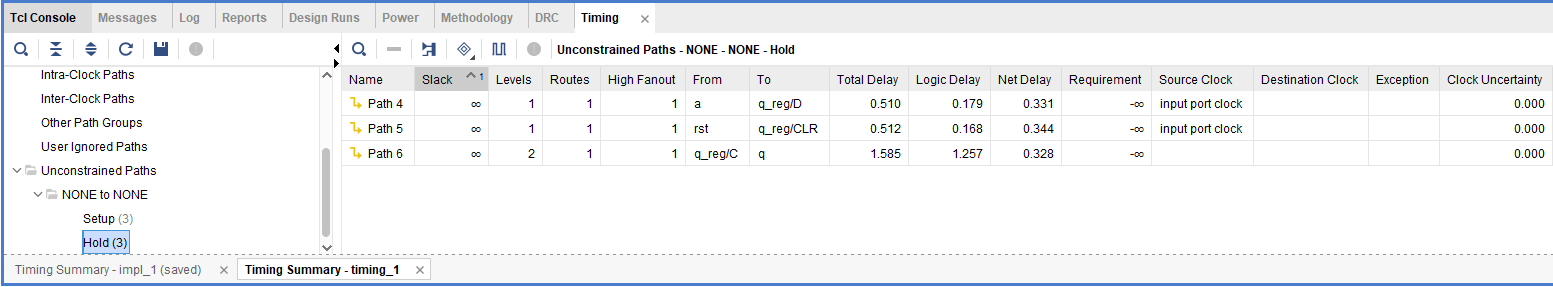

4. Report Timing Summary (Implemantation)

Report Timing Summary는 합성(synthesis)과 구현(implementation) 두 단계에서 모두 사용되며, 각 단계에서의 기능은 유사하지만 결과의 적용과 세부 정보에서 차이가 있습니다.

합성 단계의 Report Timing Summary는 설계가 로직 합성 후에 기본적인 타이밍 요구사항을 만족하는지 분석합니다. 합성 과정은 RTL(Register Transfer Level) 코드를 물리적 게이트 및 기타 하드웨어 요소로 변환하는 과정입니다. 이 단계에서의 타이밍 분석은 주로 추정치를 사용하며, 주어진 하드웨어 자원으로 설계가 목표 클록 주파수를 달성할 수 있는지 예측합니다.

- 추정된 넷(delay)과 로직(delay)을 사용: 아직 물리적 배치와 라우팅이 이루어지지 않았기 때문에, 네트워크 지연과 로직 지연은 주로 추정에 기반합니다.

- 클록 트리 미구현: 실제 클록 분배 네트워크가 구현되지 않았으므로, 클록 스큐와 같은 요소는 고려되지 않습니다.

- 타이밍 제약 확인: 사용자가 정의한 타이밍 제약을 충족하는지 확인하며, 타이밍 문제를 초기에 식별하여 수정할 수 있는 기회를 제공합니다.

구현 단계의 Report Timing Summary는 실제 물리적 배치와 라우팅이 완료된 후의 타이밍 분석을 제공합니다. 구현은 합성된 넷리스트를 사용하여 실제 칩의 물리적 구조에 따라 요소들을 배치하고 연결하는 과정입니다. 이 단계에서의 타이밍 보고서는 훨씬 더 정확하고 실제 칩 제작에 가까운 데이터를 기반으로 합니다.

- 정확한 넷(delay)과 로직(delay) 측정: 모든 물리적 배치와 라우팅이 완료되었기 때문에, 네트워크 지연과 로직 지연이 정확히 측정됩니다.

- 클록 트리 구현: 실제 클록 분배 네트워크가 구현되어 있으므로, 클록 스큐와 클록 분배 지연이 타이밍 분석에 포함됩니다.

- 팬아웃 및 전기적 효과 고려: 물리적 구현에서는 신호의 팬아웃과 전기적 효과가 포함되어, 설계의 신뢰성과 성능에 미치는 영향을 정확히 평가할 수 있습니다.

Synthesis와 Implementation에서의 Path 비교

1. 경로 및 Slack 비교

합성에서는 모든 타이밍 패스의 슬랙(Slack)이 무한대(∞)로 보고됩니다. 이는 이 단계에서는 구체적인 타이밍 제약이 설정되지 않았거나, 경로가 제약 조건 내에서 동작하고 있음을 의미할 수 있습니다.

구현에서도 모든 경로에 대한 슬랙이 무한대로 보고됩니다. 이는 실제 물리적 배치 후에도 경로들이 주어진 조건들을 만족하고 있음을 나타냅니다.

2. 총 지연(Total Delay)

합성에서는 각 경로의 총 지연이 다음과 같습니다:

- Path 1: 4.0728 ns

- Path 2: 1.846 ns

- Path 3: 1.836 ns

구현에서는 각 경로의 총 지연이 다음과 같이 상대적으로 줄어든 것을 볼 수 있습니다:

- Path 1 (Setup): 4.728 ns (증가)

- Path 2 (Setup): 1.846 ns (동일)

- Path 3 (Setup): 1.836 ns (동일)

- Path 4 (Hold): 0.510 ns

- Path 5 (Hold): 0.512 ns

- Path 6 (Hold): 1.585 ns

3. 로직 지연(Logic Delay)과 네트 지연(Net Delay)

합성과 구현에서 로직 지연과 네트 지연 모두 몇몇 경로에서 변화가 관찰됩니다. 구현 단계에서는 물리적 배치와 라우팅을 고려한 지연 측정값이 반영됩니다.

합성에서는 로직 및 네트 지연이 추정치를 바탕으로 계산됩니다.

구현에서는 물리적 라우팅 후 정확한 넷 지연을 포함하여 보고됩니다.

4. 타이밍 분석의 세밀성

합성의 타이밍 분석은 주로 넷리스트와 초기 논리 요소의 배치에 대한 추정치를 사용하며, 이는 물리적 배치와 라우팅을 고려하지 않습니다.

구현에서는 물리적 배치와 라우팅 결과를 반영한 보다 정확한 타이밍 분석을 제공합니다. 실제 물리적 거리와 연결 지연이 타이밍 분석에 포함되어 보다 현실적인 결과를 나타냅니다.

5. 타이밍 요구사항

두 단계 모두에서 실제 타이밍 제약을 적용받지 않고 있는 것으로 보이는 NONE to NONE 구성이 있습니다. 이는 설계에 타이밍 제약이 적용되지 않았거나, 해당 경로가 크리티컬하지 않다는 것을 의미할 수 있습니다.

합성과 구현 단계에서의 타이밍 정보는 설계의 진행에 따라 보다 정확하고 실제적인 결과로 발전합니다. 합성 단계에서는 경로의 타이밍을 추정하고, 구현 단계에서는 물리적 요소를 반영하여 실제 칩의 성능을 예측합니다. 설계자는 이 정보를 사용하여 성능 개선과 문제 해결에 필요한 조치를 취할 수 있습니다.

'하만 세미콘 아카데미 > Verilog HDL' 카테고리의 다른 글

| Verilog HDL 실습 (Counter) (1) | 2024.05.31 |

|---|---|

| Verilog HDL 실습 (1sec_LED) (0) | 2024.05.31 |

| Verilog HDL 실습 (Parity_bit) (0) | 2024.05.31 |

| Verilog HDL 실습 (Full Adder) (1) | 2024.05.31 |

| Vivado 사용법 및 간단한 실습 Part1 (And Gate) (0) | 2024.05.27 |