이번엔 1초마다 LED의 상태를 전환하는 디지털 타이머 회로를 구현해보겠습니다.

디지털 시스템에서 사용될 수 있으며, 특정 클록 주파수에서의 타이밍을 기반으로 작동합니다.

Verilog HDL Module Code

1sec module

`timescale 1ns / 1ps

module my_1sec(

input RST,

input CLK,

output reg LED

);

parameter clk_freq = 125_000_000;

reg enable;

reg [31:0] cnt;

always @(posedge CLK)

begin

if (RST) begin

cnt <= 32'd0;

enable <= 1'b0;

end else begin

if(cnt == (clk_freq -1)) begin

cnt <= 32'd0;

enable <= 1'b1;

end else begin

cnt <= cnt+1;

enable <= 1'b0;

end

end

end

always @(posedge CLK)

begin

if(RST)

LED <= 1'b0;

else if (enable)

LED <= ~LED;

end

endmodule

Testbench

`timescale 1ns / 1ps

module my_1sec_tb();

parameter CLK_FED = 10.0;

reg reset, clk;

wire dout;

my_1sec#( .clk_freq(10))

uut(

.RST (reset),

.CLK (clk),

.LED (dout)

);

initial begin

reset = 1'b1;

#(CLK_FED*10);

reset = 1'b0;

end

initial clk = 1'b0;

always #(CLK_FED/2) clk = ~clk;

endmodule초를 만들기 위해 먼저 주파수를 설정해줍니다.

Parameter로 125MHz를 만들어줍니다. 모듈 인스턴스화 시 주파수 값을 쉽게 조정할 수 있어 다양한 타이밍 요구 사항을 간편하게 적용할 수 있습니다.

그리고 1초를 만들어서 enable 신호를 토글해주고 enable 신호가 발생할때마다 LED 변수를 토글시킵니다.

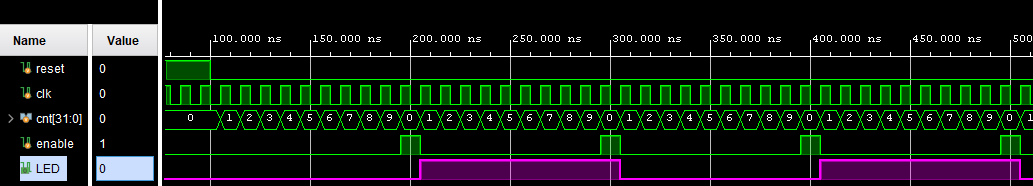

테스트 벤치에서 Enable 신호가 발생할때마다 LED가 1초마다 값이 토글되는 것으로 깜빡거리는 것을 확인할 수 있습니다.

코드를 완성하고 시뮬레이션까지 모두 확인했으니 Synthesis (합성)을 진행해줍니다.

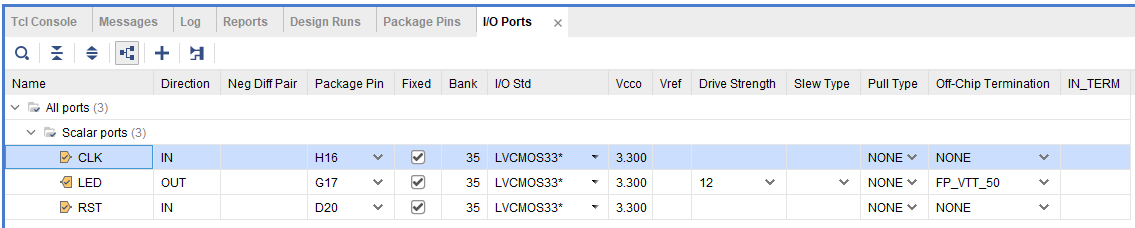

합성을 진행하고 I/O Planning 설정에서 Board에 연결을 할 수 있습니다. Package Pin 연결은 Board의 스케메틱을 보고 연결할 수 있고 제가 쓰는 보드의 전력은 3.3V 입니다. (보드마다 다르니 꼭 확인 후 설정 바랍니다.)

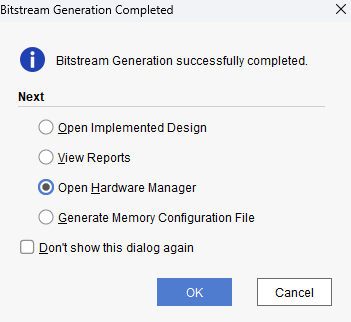

핀 설정까지 모두 마쳤으면 Implemantation과 Bitstream까지 진행해주시면 됩니다. 모두 진행하였다면 아래 화면이 뜨는데 Open Hardware Manager를 누릅니다.

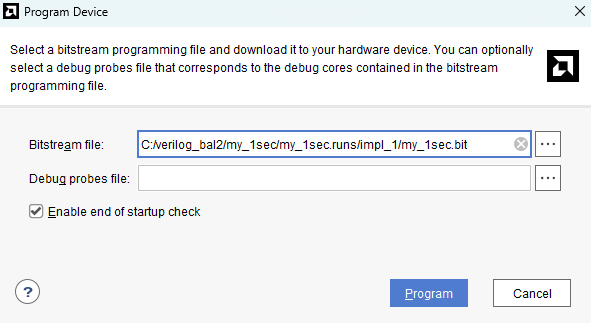

Open Target의 Auto Connect를 누르면 보드와 연결이 되고 Program Device 창에서 Program을 누르게 되면 내가 만든 회로도가 FPGA에 정상적으로 업데이트가 됩니다.

'하만 세미콘 아카데미 > Verilog HDL' 카테고리의 다른 글

| Verilog HDL 실습 (FSM) (2) | 2024.05.31 |

|---|---|

| Verilog HDL 실습 (Counter) (1) | 2024.05.31 |

| Verilog HDL 실습 (Parity_bit) (0) | 2024.05.31 |

| Verilog HDL 실습 (Full Adder) (1) | 2024.05.31 |

| Vivado 사용법 및 간단한 실습 Part2 (D Flip Flop) (1) | 2024.05.27 |