오늘은 FSM을 Verilog HDL로 만들어보겠습니다.

FSM이란?

유한 상태 기계(finite-state machine, FSM)는 컴퓨터 프로그램과 전자 논리 회로를 설계하는 데에 쓰이는 수학적 모델이다. 간단히 '상태 기계'라고 부르기도 한다. 많은 디지털 시스템에서 System 및 Data Flow Path의 동작을 제어하는 데 사용되는 Sequential 회로입니다.

현재 상태 Current state 와 input에 따라 다음 상태 Next state가 결정이 됩니다. Verilog로 컨트롤러를 설계한다고 했을 때 FSM을 이용하면 비교적 쉽게 설계할 수 있습니다. If else 분기문을 통해서 설계할 수 있으나 HW는 동시성의 개념이 있기 때문에 If else를 여기저기 남발하다가 나도 모르는 사이에 코드가 꼬이는 경험이 될 수 있습니다.

하나의 FSM Logic은 하나의 상태만을 가지게 되고 어떠한 사건에 의해 현 상태에서 다른 상태로 변화할 수 있는데. 이를 Transition이라고 부릅니다.

Verilog HDL Code

FSM Module

`timescale 1ns / 1ps

module my_fsm(

input RST,

input CLK,

input [1:0] SW,

output reg [1:0] LED,

output VCC

);

assign VCC = 1'b1;

localparam [1:0] idle = 2'b00,

state_a = 2'b01,

state_b = 2'b10,

state_c = 2'b11;

reg [1:0] curr_state, next_state;

always @(posedge CLK)

begin

if(RST)

curr_state <= idle;

else

curr_state <= next_state;

end

always @(curr_state, SW)

begin

case (curr_state)

idle : begin

if(SW == 2'b01)

next_state = state_a;

else

next_state = idle;

LED = 2'b00;

end

state_a : begin

if(SW == 2'b10)

next_state = state_b;

else

next_state = state_a;

LED = 2'b01;

end

state_b : begin

if(SW == 2'b11)

next_state = state_c;

else

next_state = state_b;

LED = 2'b10;

end

state_c : begin

if(SW == 2'b00)

next_state = idle;

else

next_state = state_c;

LED = 2'b11;

end

default : next_state = idle;

endcase

end

endmodule

Testbench

`timescale 1ns / 1ps

module my_fsm_tb();

parameter CLK_PD = 10.0;

reg RST, CLK;

reg [1:0] SW;

wire [1:0] led;

my_fsm uut(

.RST (RST),

.CLK (CLK),

.SW (SW),

.LED (led)

);

initial begin

RST = 1'b1;

#(CLK_PD*20);

RST = 1'b0;

end

initial CLK = 1'b0;

always #(CLK_PD/2) CLK = ~CLK;

initial begin

SW = 2'b00;

wait (RST <= 1'b0);

#(CLK_PD*10);

SW = 2'b01;

#(CLK_PD*10);

SW = 2'b10;

#(CLK_PD*10);

SW = 2'b11;

#(CLK_PD*10);

SW = 2'b00;

end

endmodule

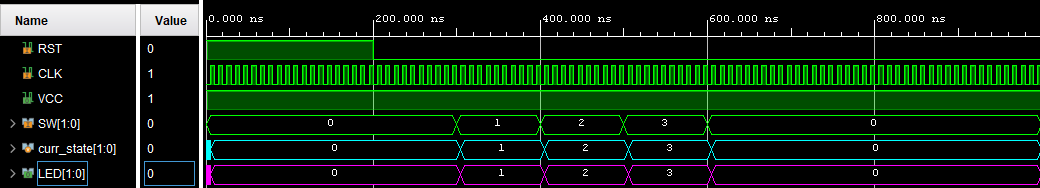

이번 실습은 버튼을 누르면 다음 상태로 전환되는 기능을 만들어보려고 합니다. 버튼의 입력에 따라 상태가 넘어가고 상태마다 각각 LED가 켜짐으로써 FSM이 잘 동작하는지 확인합니다. 보드 테스트 전에 Simulation으로 먼저 이상이 없는지부터 감지합니다.

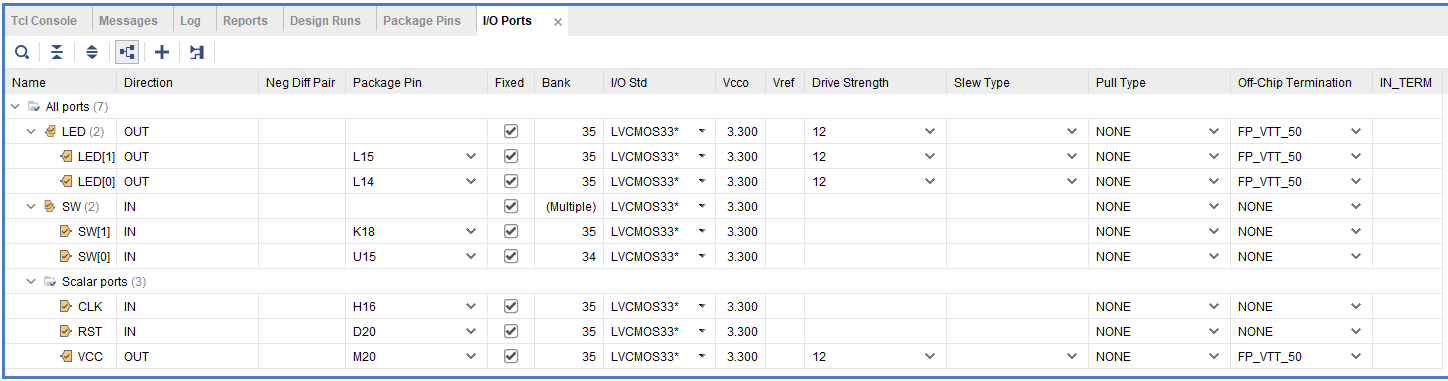

Simulation에서 스위치의 2진수 값에 따라 상태 변화가 잘 바뀌는 것을 볼 수 있습니다. 그에따라 LED도 안정적으로 변화하고 있습니다. Simulation까지 마치면 Synthesis를 진행하여 핀 배치를 해줍니다. 핀 배치를 해줄때는 각 보드의 schematic을 확인하여 해줍니다.

Bitstream까지 진행후 보드와 연결하여 FPGA에서 테스트 합니다.

'하만 세미콘 아카데미 > Verilog HDL' 카테고리의 다른 글

| Verilog HDL 실습 (Traffic) (1) | 2024.05.31 |

|---|---|

| Verilog HDL 실습 (Security) (0) | 2024.05.31 |

| Verilog HDL 실습 (Counter) (1) | 2024.05.31 |

| Verilog HDL 실습 (1sec_LED) (0) | 2024.05.31 |

| Verilog HDL 실습 (Parity_bit) (0) | 2024.05.31 |