오늘은 간단한 보안 장치를 Verilog HDL로 만들어보겠습니다.

키를 작동시키게 되면 감지 구간으로 진입하여 일정한 시간내로 버튼을 누르지 않으면 알람이 울리는 형태로 만들어보도록 하겠습니다. 실제 부저를 부착하는 대신 LED로 대신하여 제작해보도록 하겠습니다.

보안 시스템의 주요 동작을 구현한 것으로, FSM (유한 상태 기계)을 사용하여 시스템의 상태를 관리합니다. 시스템은 클록 신호(CLK), 리셋 신호(RST), 사용자 입력 키(KEY), 그리고 센서 입력(SENSOR)에 의해 제어됩니다. 이 시스템은 네 가지 주요 상태를 가지며, 각 상태는 알람 시스템의 동작을 결정합니다.

Security Module

`timescale 1ns / 1ps

module my_security(

input RST,

input CLK,

input [1:0] KEY,

input SENSOR,

(*mark_debug = "true" *)

output reg ALARM_SIREN,

output reg [1:0] FSM_STATE

);

parameter CLK_FREQ = 125_000_000;

localparam [1:0] disarmed = 2'b00,

armed = 2'b01,

wait_delay = 2'b10,

alarm = 2'b11;

(* MARK_DEBUG="true" *)

reg [1:0] curr_state, next_state;

(*mark_debug = "true" *)

wire cnt_done;

(*mark_debug = "true" *)

reg start_cnt;

(*mark_debug = "true" *)

reg [29:0] cnt;

always @(posedge CLK)

if(RST)

curr_state <= disarmed;

else

curr_state <= next_state;

always @(curr_state, KEY, SENSOR, cnt_done)

begin

start_cnt = 1'b0;

ALARM_SIREN = 1'b0;

case(curr_state)

disarmed : begin

if(KEY == 2'b11)

next_state = armed;

else

next_state = disarmed;

FSM_STATE = 2'b00;

end

armed : begin

if(SENSOR == 1'b1)

next_state = wait_delay;

else if (KEY == 2'b00)

next_state = disarmed;

else

next_state = armed;

FSM_STATE = 2'b01;

end

wait_delay : begin

start_cnt = 1'b1;

if(cnt_done == 1'b1)

next_state = alarm;

else if (KEY == 2'b00)

next_state = disarmed;

else

next_state = wait_delay;

FSM_STATE = 2'b10;

end

alarm : begin

ALARM_SIREN = 1'b1;

if(KEY == 2'b00)

next_state = disarmed;

else

next_state = alarm;

FSM_STATE = 2'b11;

end

default : next_state = disarmed;

endcase

end

always @(posedge CLK)

begin

if (RST)

cnt <= 30'd0;

else if(start_cnt)

cnt <= cnt + 1;

else

cnt <= 30'd0;

end //always

assign cnt_done = cnt == (CLK_FREQ*5 -1);

endmoduleTestbench

`timescale 1ns / 1ps

module my_security_tb();

parameter CLK_PD = 8.00;

reg RST, CLK;

reg [1:0] KEY;

reg SENSOR;

wire alarm_siren;

wire [1:0] fsm_state;

my_security #(.CLK_FREQ(10))

uut (

.RST (RST),

.CLK (CLK),

.KEY (KEY),

.SENSOR (SENSOR),

.ALARM_SIREN (alarm_siren),

.FSM_STATE (fsm_state)

);

initial begin

RST = 1'b1;

#(CLK_PD*10);

RST = 1'b0;

end

initial CLK = 1'b0;

always #(CLK_PD/2) CLK = ~CLK;

initial begin

KEY = 2'b00;

SENSOR = 1'b0;

wait (RST == 1'b0);

#(CLK_PD*10);

KEY = 2'b11; // armed

#(CLK_PD*10);

KEY = 2'b00; // disarmed

#(CLK_PD*10);

KEY = 2'b11; // armed

#(CLK_PD*10);

SENSOR = 1'b1;

wait (alarm_siren == 1'b1);

SENSOR = 1'b0;

#(CLK_PD*10);

KEY = 2'b00; //disarmed

#(CLK_PD*10);

$finish;

end

endmodule

RST: 리셋 입력으로, 시스템을 초기 상태(disarmed)로 리셋합니다.

CLK: 클록 신호로, 시스템의 타이밍을 제어합니다.

KEY: 사용자 입력 키로, 시스템을 무장, 해제 또는 다른 상태로 전환하는 데 사용됩니다.

SENSOR: 보안 센서에서 감지된 입력으로, 보안 위협을 감지하는 데 사용됩니다.

ALARM_SIREN: 알람이 활성화되었을 때 1로 설정되어 경보를 울립니다.

FSM_STATE: 현재 FSM의 상태를 나타내는 2비트 출력입니다.

Disarmed (2'b00):

시스템이 무장 해제된 상태입니다.

KEY가 2'b11로 설정되면 시스템은 armed 상태로 전환됩니다.

Armed (2'b01):

시스템이 무장된 상태입니다.

센서가 활성화(1'b1)되면 wait_delay 상태로 전환됩니다.

KEY가 2'b00으로 설정되면 시스템은 다시 disarmed 상태로 돌아갑니다.

Wait_delay (2'b10):

센서가 활성화된 후 일정 시간 동안 대기하는 상태입니다.

설정된 시간(5초)이 경과하면 alarm 상태로 전환됩니다.

KEY가 2'b00으로 설정되면 disarmed 상태로 전환됩니다.

Alarm (2'b11):

알람이 울리는 상태입니다.

이 상태에서는 ALARM_SIREN이 활성화됩니다.

KEY가 2'b00으로 설정되면 disarmed 상태로 전환됩니다.

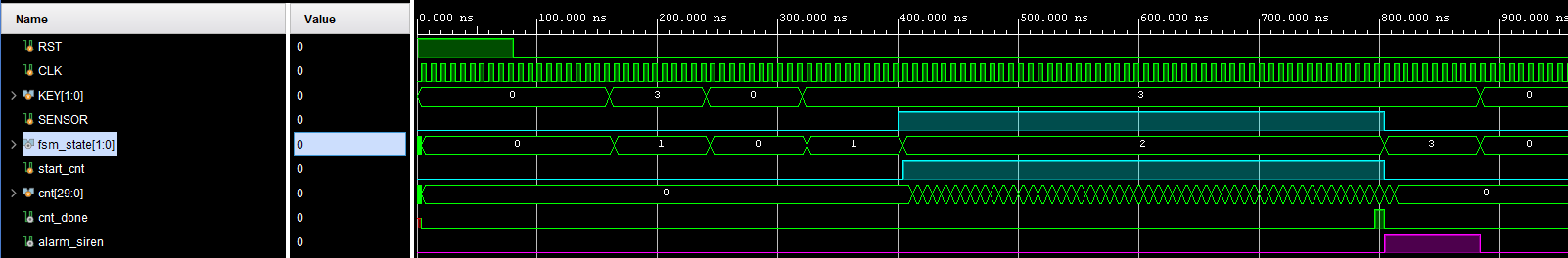

카운터 및 타이밍 Simulation

카운터(cnt): wait_delay 상태에서 활성화되며, 설정된 시간 동안 세어집니다.

cnt_done: 카운터가 설정된 시간(예: 5초)에 도달하면 활성화되어 상태 전환의 조건으로 사용됩니다.

Synthesis 후에 오류가 없으면 Pin을 설정해줍니다.

Bitstream 후 FPGA 보드에서 테스트를 해보았습니다.

수업시간에 진행한 Security Module은 생각해보니 부족한 부분이 많은 거 같아서 추후에 혼자서 다시 업그레이드 하여 제작해보려고 합니다.

'하만 세미콘 아카데미 > Verilog HDL' 카테고리의 다른 글

| Verilog HDL 실습 (Stop_Watch) (0) | 2024.05.31 |

|---|---|

| Verilog HDL 실습 (Traffic) (0) | 2024.05.31 |

| Verilog HDL 실습 (FSM) (0) | 2024.05.31 |

| Verilog HDL 실습 (Counter) (0) | 2024.05.31 |

| Verilog HDL 실습 (1sec_LED) (0) | 2024.05.31 |